SK하이닉스, HBM4용 장비로 '플럭스리스 본더' 도입 검토 [소부장반차장]

- 가

- 가

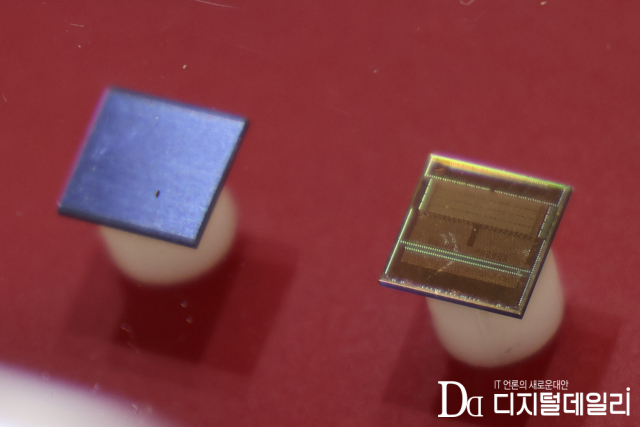

SK하이닉스는 지난 4일(현지시간) 대만 타이베이 난강전람관에서 개최된 컴퓨텍스 2024에 참가해 36GB(기가바이트) 12단 HBM3E를 전시했다.

[디지털데일리 고성현 기자] SK하이닉스가 6세대 고대역폭메모리(HBM)인 'HBM4' 등에 활용할 장비로 플럭스리스(Fluxless) 본더 적용을 고려하고 있다. 차세대 장비로 꼽히는 하이브리드(Hybrid) 본더가 당장 도입하기 어려운 만큼, 중간 다리 역할을 하는 공정을 적용하겠다는 의미로 해석된다.

15일 업계에 따르면 SK하이닉스는 HBM4에 플럭스리스 본딩 공정을 적용하는 것을 검토하고 있다. 당장 도입해 투입하는 것이 아닌 연구개발(R&D) 차원에서 사업성을 검토하는 단계로 알려졌다. HBM4가 HBM3E 대비 단수가 4단 이상 늘어날 수 있는 만큼, D램 간 간격(Pitch)을 줄이기 위해 이를 고려하는 것으로 풀이된다.

SK하이닉스가 HBM 생산을 위해 채택한 어드밴스드 매스리플로우-몰디드언더필(Advanced MR-MUF) 방식은 마이크로 범프를 부착한 칩에 플럭스를 도포한 다음, 수직으로 칩을 하나씩 쌓으며 열압착(TC) 본더를 활용해 임시 접합하는 과정을 거친다. 이후 리플로우 과정을 거쳐 칩 전체를 접합하고 밀봉재와 몰딩을 주입한 다음 TC 본더로 열과 압력을 가해 이를 굳혀 완성한다.

이 과정에서 플럭스를 사용하면 범프와 패드의 비교적 정확한 정렬(Align)과 고정이 가능하다는 장점이 있다. 하지만 세정 시 잔여물이 남을 수 있어 수율 등에 영향을 미칠 수 있다는 단점도 남아 있다.

특히 플럭스가 HBM4 등 D램 적층 단수가 늘어나는 차세대 제품에서도 불리하게 작용할 수 있다는 우려가 나온다. 현재 12단인 HBM3E는 6세대인 HBM4에서는 최대 16단으로 적층 수가 늘어나는데, 최종 패키지 두께는 HBM3E(720㎛)보다 살짝 높은 775마이크로미터(㎛) 수준으로 맞춰야 한다. 이때 플럭스 활용을 유지하게 되면 칩과 칩 사이 간격을 좁히기가 어렵다.

이를 해결할 대안으로 꼽혔던 공정은 하이브리드 본딩이다. 범프를 사용하는 대신 구리와 구리를 직접 붙여 칩과 칩 간격을 크게 줄일 수 있는 덕이다. 하지만 미비한 표준과 높은 기술적 난제 및 제조 비용으로 인해 당장 적용이 어려운 것으로 평가 받는다. 이에 따라 플럭스를 없애 간격을 줄이는 플럭스리스 본딩 방식이 새롭게 고려되고 있는 것이다.

반도체 업계는 플럭스리스 본딩이 도입되면 적층 D램 칩과 칩 간 간격을 좁힐 수 있어 효율적으로 두께를 줄일 수 있을 것으로 내다봤다. SK하이닉스가 HBM4까지 어드밴스드 MR-MUF 방식을 유지한다는 점을 고려하면, 이 방식이 하이브리드 본딩 전 단계로 활용할 가능성이 높다는 관측이다.

SK하이닉스 등의 공정 방식 변화에 따라 TC 본더 장비사들도 관련 제품 상용화를 준비하고 있다. 네덜란드 장비사인 ASMPT는 플럭스리스 본더를 출시해 HBM 대응에 나섰으며, 일본 신카와 역시 이미 확보한 요소 기술을 활용해 이를 개발 중인 것으로 알려졌다.

국내 장비사인 한미반도체는 최근 TC 본더 개발 로드맵을 공개하며 플럭스리스 장비 개발을 시사했다. 회사는 2026년 하반기 출시를 목표로 하이브리드 본더를 개발하는 한편 내년 하반기까지 '마일드 하이브리드 본더'를 개발하겠다는 목표를 내놨다. 마일드 하이브리드 본더는 하이브리드 본딩 이전 중간 단계의 장비로, 플럭스리스 본더를 의미하는 것으로 풀이된다.

한편 SK하이닉스 관계자는 이와 관련해 "HBM4 관련 다양하게 검토하고 있는 기술 중 하나이나 아직 확정적이거나 구체화된 부분은 없다"고 말했다.

이 기사와 관련된 기사

당신이 좋아할 만한 뉴스

많이 본 기사

연재기사

실시간 추천 뉴스

-

네이버 웹툰엔터, 1분기 영업적자 387억원…"2분기 글로벌 확장 나설 것"

2025-05-14 07:11:56 -

크립토닷컴, 케이에스넷과 암호화폐 결제서비스 파트너십 체결

2025-05-13 17:30:07 -

"하필 대선 기간때"… MG손보 노조, ‘일부 영업 정지’·‘폐쇄형 가교 보험사’ 금융위 방안에 강력 반발

2025-05-13 17:17:31 -

'스테이블코인' 대선 이슈 선점나선 민주당… 윤여준 "디지털자산 글로벌 허브로 도약"

2025-05-13 16:50:19 - 2025-05-13 16:48:34